back to overview ^

» DVM Test Report: VOUT=1.505V|Bode Plot|Vin Nominal|100% Load

| Test Details | |

| Schematic | 6.3_LTC3406B - DVM ADVANCED.sxsch |

| Test | VOUT=1.505V|Bode Plot|Vin Nominal|100% Load |

| Date / Time | 4/22/2013 4:54:39 PM |

| Report Directory | DVM_REPORTS\2013-04-22-4_54_19_PM\VOUT=1.505V\Bode Plot\Vin Nominal\100% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 66.2768% |

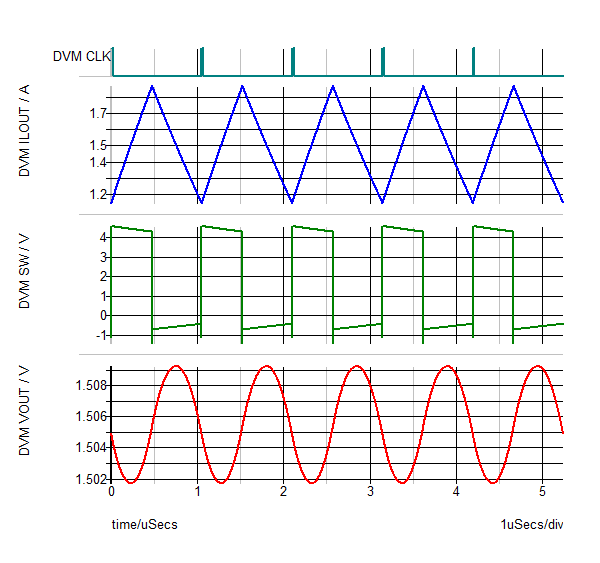

| Frequency(CLK) | 955.63357kHertz |

| Power(LOAD) | 2.25923 |

| Power(SRC) | 3.40878 |

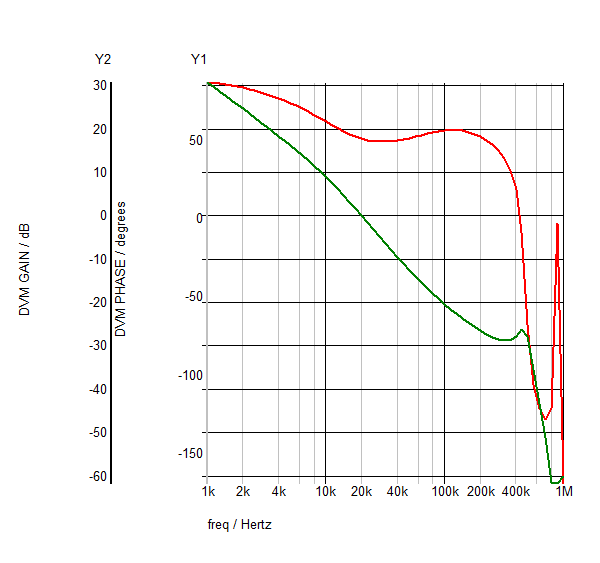

| gain_crossover_freq | 19.8447k |

| gain_margin | 26.7773 |

| min_phase | 50.9045 |

| phase_crossover_freq | 432.886k |

| min_phase_freq | 19.8447k |

| phase_margin | 50.895 |

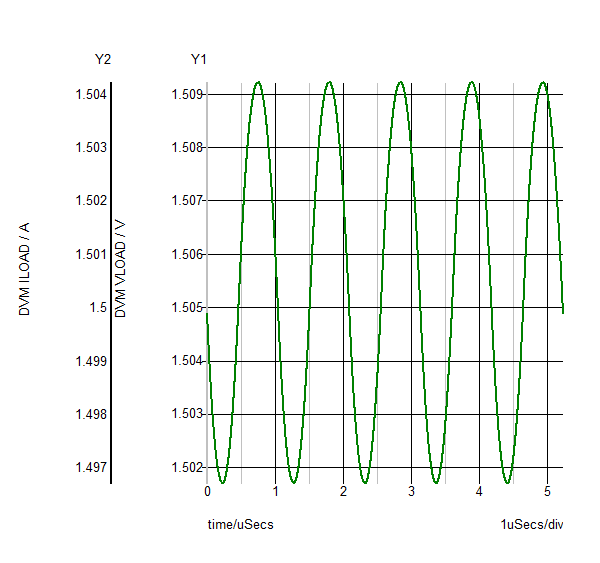

| ILOAD | AVG 1.50058 MIN 1.4967 MAX 1.50421 RMS 1.50058 |

| ILOUT | AVG 1.50058 MIN 1.14273 MAX 1.86156 RMS 1.51489 |

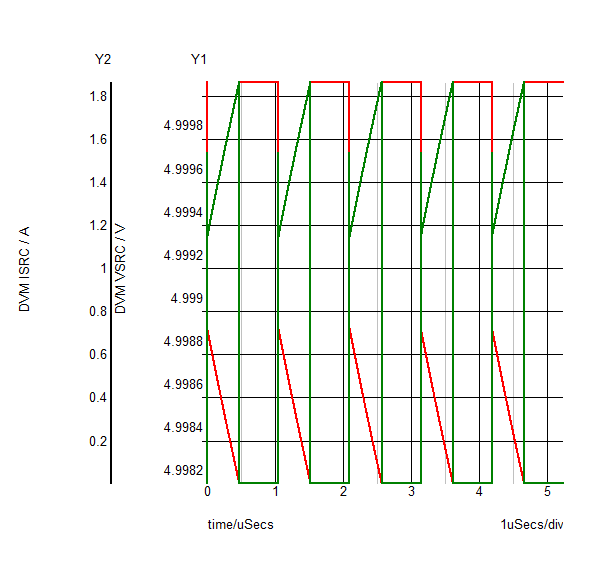

| ISRC | AVG 681.965m MIN 423.722u MAX 1.86199 RMS 1.02424 |

| SW | AVG 1.65563 MIN -1.44462 MAX 4.54153 RMS 2.98569 |

| VLOAD | AVG 1.50557 MIN 1.50168 MAX 1.50921 RMS 1.50557 |

| VOUT | AVG 1.50557 MIN 1.50168 MAX 1.50921 RMS 1.50557 |

| VSRC | AVG 4.99932 MIN 4.99814 MAX 5 RMS 4.99932 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (1.50921) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | PASS: Min. Output1 Voltage (1.50168) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (26.7773) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (50.895) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac7_318.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop7_301.sxgph |

SRC

ISRC

VSRC

|

|

| SXGPH File | simplis_pop7_291.sxgph |

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop7_296.sxgph |

| Other SXGPH Files | |

| DVM Bode Plot Input#log#ac | simplis_ac7_325.sxgph |

| clock#pop | simplis_pop7_283.sxgph |