back to overview ^

» DVM Test Report: Pre-Process

| Test Details | |

| Schematic | 6.3_LTC3406B - DVM ADVANCED.sxsch |

| Test | Pre-Process |

| Date / Time | 4/30/2013 3:20:51 PM |

| Report Directory | DVM_REPORTS\2013-04-30-3_20_49_PM\Pre-Process |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Frequency(CLK) | 955.63308kHertz |

| GAIN | MIN -61.6648 MAX 30.3333 |

| ILOAD | MIN 1.49635 MAX 1.50441 |

| ILOUT | MIN 1.11755 MAX 1.89 |

| ISRC | MIN 466.041u MAX 1.89047 |

| PHASE | MIN -168.703 MAX 86.7445 |

| SW | MIN -1.456 MAX 5.05159 |

| VLOAD | MIN 1.50133 MAX 1.50942 |

| VOUT | MIN 1.50133 MAX 1.50942 |

| VSRC | MIN 5.49811 MAX 5.5 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (1.50942) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | PASS: Min. Output1 Voltage (1.50133) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

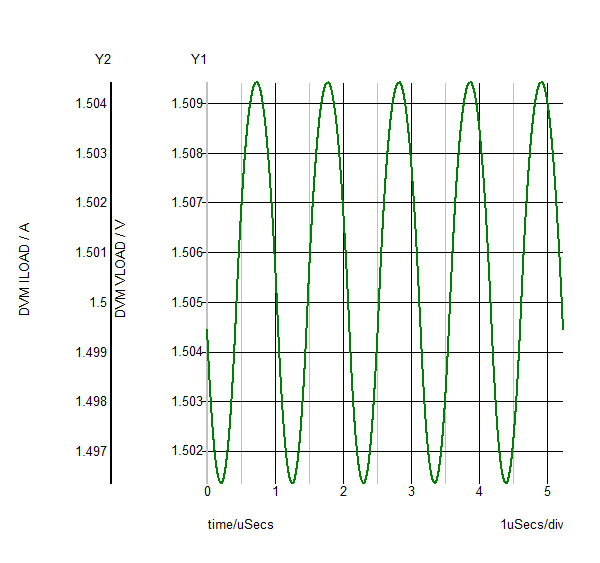

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop39_1805.sxgph |

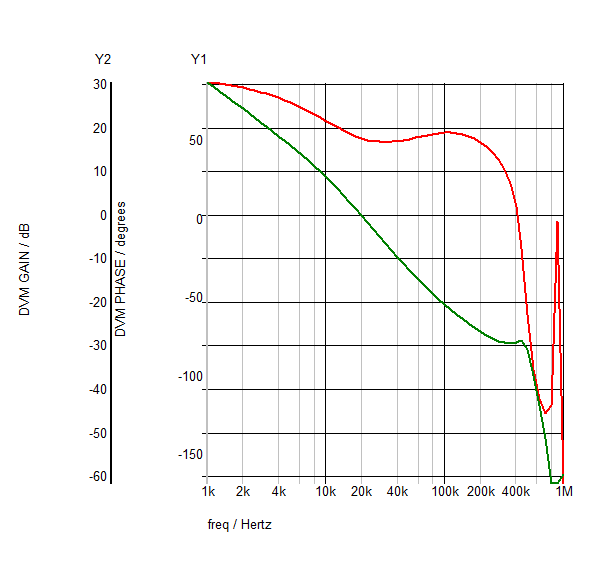

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac39_1822.sxgph |

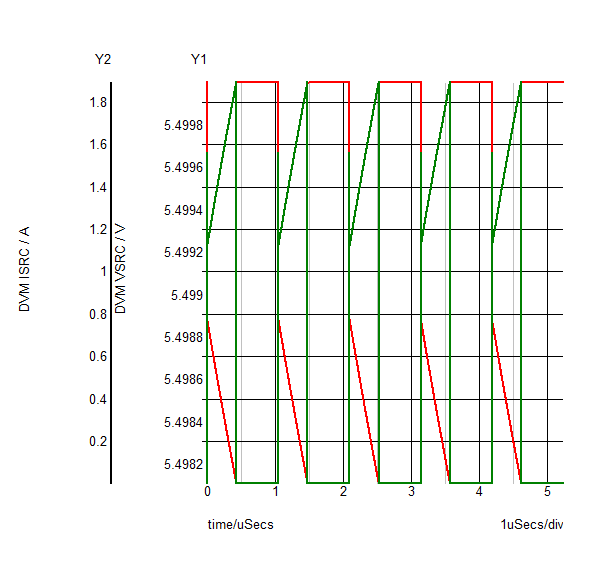

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop39_1795.sxgph |

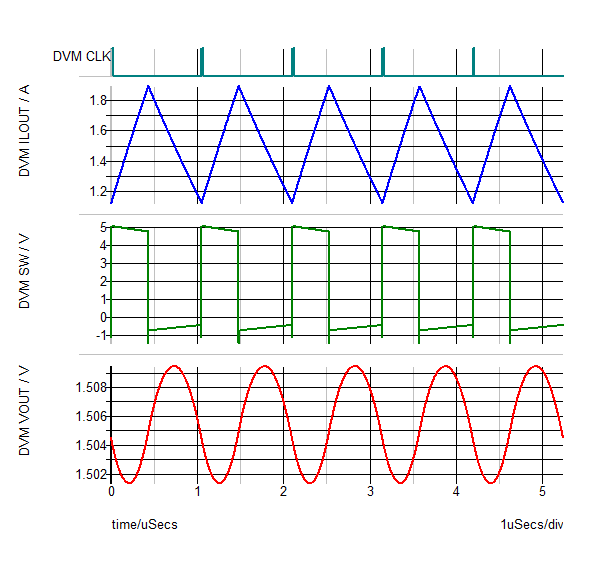

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop39_1800.sxgph |

| Other SXGPH Files | |

| DVM Bode Plot Input#log#ac | simplis_ac39_1829.sxgph |

| clock#pop | simplis_pop39_1787.sxgph |