# **SIMETRIX**

# SPICE AND MIXED MODE SIMULATION

SIMULATOR REFERENCE MANUAL

# Copyright ©1992-2012 SIMetrix Technologies Ltd.

### **Trademarks**

PSpice is a trademark of Cadence Design Systems Inc. Hspice is a trademark of Synopsis Inc.

### Contact

SIMetrix Technologies Ltd., 78 Chapel Street, Thatcham, RG18 4QN, United Kingdom

Tel.: +44 1635 866395 Fax: +44 1635 868322 Email: info@simetrix.co.uk

Internet http://www.simetrix.co.uk

Copyright © SIMetrix Technologies Ltd. 1992-2012 SIMetrix Simulator Reference Manual 30/10/2012

# **Table of Contents**

| Chapter 1 | Introduction                                         |       |

|-----------|------------------------------------------------------|-------|

|           | Overview                                             | 12    |

|           | The SIMetrix Simulator - What is it?                 |       |

|           | What is in This Manual                               |       |

|           | What is in this Marian                               | 12    |

| Chapter 2 | Running the Simulator                                |       |

|           | Using the Simulator with the SIMetrix Schematic Edit | or 13 |

|           | Adding Extra Netlist Lines                           | 13    |

|           | Displaying Net and Pin Names                         | 13    |

|           | Editing Device Parameters                            |       |

|           | Editing Literal Values - Using shift-F7              |       |

|           | Running in non-GUI Mode                              | 15    |

|           | Overview                                             |       |

|           | Important Licensing Information                      |       |

|           | Syntax                                               |       |

|           | Aborting                                             |       |

|           | Reading Data                                         |       |

|           | Configuration Settings                               |       |

|           | Netlist Format                                       | 20    |

|           | File Format                                          | 21    |

|           | Language Declaration                                 |       |

|           | Comments                                             |       |

|           | Device Lines                                         |       |

|           | Simulator Statements                                 | 24    |

|           | Simulator Output                                     | 24    |

|           | The List File                                        |       |

|           | The Binary Data File                                 |       |

|           | Output Data Names                                    |       |

|           | Data Handling - Controlling Data Saved               |       |

| Chapter 3 | Simulator Devices                                    |       |

|           | Overview                                             | 29    |

|           | Using XSPICE Devices                                 |       |

|           | Vector Connections                                   |       |

|           | Connection Types                                     |       |

|           | Using Expressions                                    |       |

|           | Overview                                             |       |

|           | Using Expressions for Device Parameters              |       |

|           | Joing Expressions for Dovido Faramotold              |       |

|           | Using Expressions for Model Parameters                    | 32   |

|-----------|-----------------------------------------------------------|------|

|           | Expression Syntax                                         | 32   |

|           | Optimisation                                              | 43   |

|           | Subcircuits                                               |      |

|           | Overview                                                  |      |

|           | Subcircuit Definition                                     | . 44 |

|           | Subcircuit Instance                                       |      |

|           | Passing Parameters to Subcircuits                         | . 46 |

|           | Nesting Subcircuits                                       |      |

|           | Global Nodes                                              |      |

|           | Subcircuit Preprocessing                                  |      |

|           | Model Binning                                             |      |

|           | Overview                                                  |      |

|           | Defining Binned Models                                    |      |

|           | Example                                                   | . 48 |

|           | Language Differences                                      |      |

|           | Inline Comment                                            |      |

|           | Unlabelled Device Parameters                              | . 49 |

|           | LOG() and PWR()                                           |      |

|           | Customising Device Configuration                          | . 50 |

|           | Overview                                                  |      |

|           | What does the Device Configuration File do?               |      |

|           | Creating a Device Configuration File                      |      |

|           | List of All Simulator Devices                             | . 52 |

|           |                                                           |      |

| Chapter 4 | Analog Device Reference                                   |      |

| •         | •                                                         |      |

|           | Overview                                                  |      |

|           | Further Documentation                                     |      |

|           | AC Table Lookup (including S-Parameters)                  |      |

|           | AC Table Notes                                            |      |

|           | Arbitrary Source                                          |      |

|           | Notes on Arbitrary Expression                             |      |

|           | Charge and Flux Devices                                   |      |

|           | Arbitrary Source Examples                                 |      |

|           | PSpice and Hspice syntax                                  |      |

|           | Bipolar Junction Transistor (SPICE Gummel Poon)           |      |

|           | Notes                                                     |      |

|           | Bipolar Junction Transistor (VBIC without self heating) . |      |

|           | Notes                                                     |      |

|           | Bipolar Junction Transistor (VBIC with self heating)      |      |

|           | Notes                                                     |      |

|           | Bipolar Junction Transistor (MEXTRAM)                     |      |

|           | Bipolar Junction Transistor (HICUM)                       | 72   |

| Capacitor                         |     |

|-----------------------------------|-----|

| Current Controlled Current Source |     |

| Polynomial Specification          | 75  |

| Current Controlled Voltage Source | 76  |

| Current Source                    | 76  |

| Diode - Level 1 and Level 3       | 77  |

| Diode - Soft Recovery             | 81  |

| Basic Equations                   | 82  |

| References                        |     |

| GaAsFET                           | 83  |

| Inductor (Ideal)                  |     |

| Inductor (Saturable)              |     |

| Notes on the Jiles-Atherton model |     |

| Notes on the non-hysteresis model |     |

| Implementing Transformers         |     |

| Plotting B-H curves               |     |

| References                        |     |

| Insulated Gate Bipolar Transistor |     |

| Junction FET                      | 89  |

| Lossy Transmission Line           |     |

| MOSFET                            |     |

| BSIM3 MOSFETs                     |     |

| Notes                             |     |

| Version Selector                  |     |

| Model Parameters                  | 101 |

| Further Documentation             |     |

| Process Binning                   |     |

| BSIM4 MOSFETs                     |     |

| Notes                             |     |

| Further Documentation             |     |

| Process Binning                   | 103 |

| EKV MOSFETs                       |     |

| Notes                             |     |

| HiSim HV MOSFET                   |     |

| Notes                             |     |

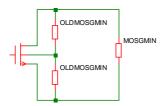

| MOSFET GMIN Implementation        |     |

| PSP MOSFET                        |     |

| Resistor                          |     |

| Resistor - Hspice Compatible      |     |

| Resistance Calculation            |     |

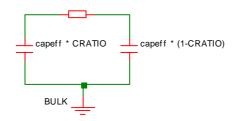

| Capacitance Calculation           |     |

| Temperature Scaling               |     |

| Flicker Noise                     |     |

| ACRESMOD Parameter                | 112 |

| Making the Hspice Resistor the Default                |

|-------------------------------------------------------|

| CMC Resistor                                          |

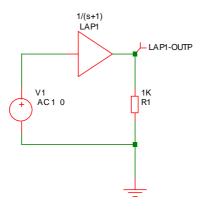

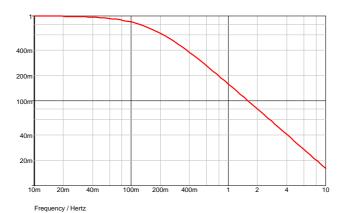

| S-domain Transfer Function Block 113                  |

| Description114                                        |

| Examples 115                                          |

| The Laplace Expression118                             |

| Defining the Laplace Expression Using Coefficients119 |

| Other Model Parameters119                             |

| Limitations119                                        |

| The XSPICE S_XFER model119                            |

| Subcircuit Instance                                   |

| Transmission Line                                     |

| Example 121                                           |

| Voltage Controlled Current Source 121                 |

| Voltage Controlled Switch 122                         |

| Voltage Controlled Switch Notes122                    |

| Voltage Controlled Voltage Source 123                 |

| Voltage Source123                                     |

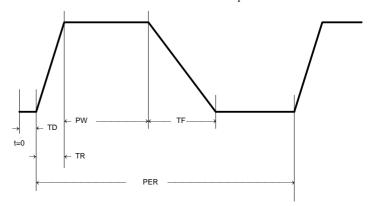

| Pulse Source124                                       |

| Piece-Wise Linear Source126                           |

| PWL File Source126                                    |

| Sinusoidal Source127                                  |

| Exponential Source128                                 |

| Single Frequency FM129                                |

| Noise Source129                                       |

| Extended PWL Source129                                |

| Mutual Inductor131                                    |

| Notes                                                 |

| Example                                               |

| Verilog-HDL Interface (VSXA)132                       |

| Overview                                              |

| Analog Input Interface135                             |

| Analog Output Interface136                            |

| Data Vector Output136                                 |

| Module Cache137                                       |

| NXP Compact Models                                    |

| Introduction                                          |

| SIMKIT Devices                                        |

| Notes on SIMKIT Models142                             |

| PCM Devices143                                        |

| Notes on PCM Models 144                               |

| Documentation 144                                     |

| Chapter 5 | Digital/Mixed Signal Device Refere | nce |

|-----------|------------------------------------|-----|

|           | Digital Device Overview            | 145 |

|           | Common Parameters                  |     |

|           | Delays                             |     |

|           | And Gate                           | 146 |

|           | D-type Latch                       | 148 |

|           | D-type Flip Flop                   |     |

|           | Buffer                             | 152 |

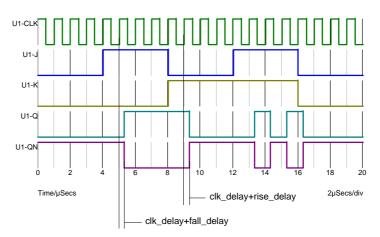

|           | Frequency Divider                  | 153 |

|           | Digital Initial Condition          | 155 |

|           | Digital Pulse                      | 156 |

|           | Digital Signal Source              | 157 |

|           | Inverter                           | 160 |

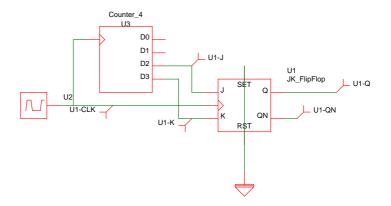

|           | JK Flip Flop                       | 161 |

|           | Arbitrary Logic Block              |     |

|           | Nand Gate                          |     |

|           | Nor Gate                           |     |

|           | Open-Collector Buffer              |     |

|           | Open-Emitter Buffer                |     |

|           | Or Gate                            |     |

|           | Pulldown Resistor                  |     |

|           | Pullup Resistor                    |     |

|           | Random Access Memory               |     |

|           | Set-Reset Flip-Flop                |     |

|           | SR Latch                           |     |

|           | State Machine                      |     |

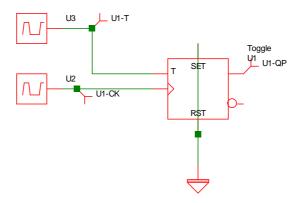

|           | Toggle Flip Flop                   |     |

|           | Tri-State Buffer                   |     |

|           | Exclusive NOR Gate                 |     |

|           | Exclusive OR Gate                  |     |

|           | Analog-Digital Converter           |     |

|           | Analog-Digital Interface Bridge    |     |

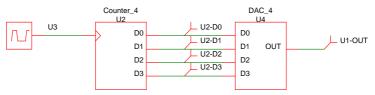

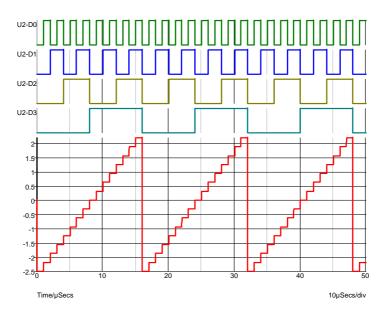

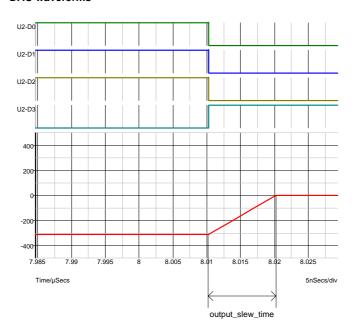

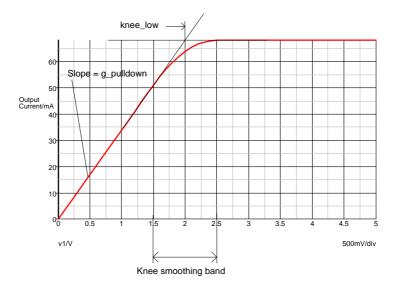

|           | Digital-Analog Converter           |     |

|           | Digital-Analog Interface Bridge    |     |

|           | Controlled Digital Oscillator      |     |

|           | Analog-Digital Schmitt Trigger     | 202 |

| Chapter 6 | Command Reference                  |     |

|           | Overview                           | 204 |

|           | General Sweep Specification        |     |

|           | Overview                           |     |

|           | Syntax                             |     |

|           | •                                  |     |

| Multi Step Analyses                           | 207 |

|-----------------------------------------------|-----|

| Overview                                      | 207 |

| Syntax                                        | 207 |

| .AC                                           | 209 |

| .ALIAS                                        | 210 |

| .DC                                           | 211 |

| .FILE and .ENDF                               |     |

| .FUNC                                         | 214 |

| .GLOBAL                                       |     |

| .GRAPH                                        |     |

| Parameters                                    |     |

| Using Multiple .GRAPH Statements              |     |

| Creating X-Y Plots                            |     |

| Using .GRAPH in Subcircuits                   |     |

| Using Expressions with .GRAPH                 |     |

| Plotting Spectra with .GRAPH                  |     |

| .IC                                           |     |

| Alternative Initial Condition Implementations | 222 |

| .INC                                          |     |

| KEEP                                          |     |

| Option Settings                               |     |

| LOAD                                          |     |

| .LIB                                          |     |

| SIMetrix Native Form                          |     |

| HSPICE Form                                   |     |

| .MODEL                                        |     |

| .NOCONV                                       |     |

| .NODESET                                      |     |

| .NOISE                                        |     |

| .OP                                           |     |

| OPTIONS                                       |     |

| .PARAM                                        |     |

| .POST_PROCESS                                 |     |

| .PRINT                                        |     |

| SENS                                          |     |

| SETSOA                                        |     |

| Examples                                      |     |

| .SUBCKT and .ENDS                             | 261 |

| .TEMP                                         |     |

| .TF                                           |     |

| TRACE                                         |     |

| TRAN                                          |     |

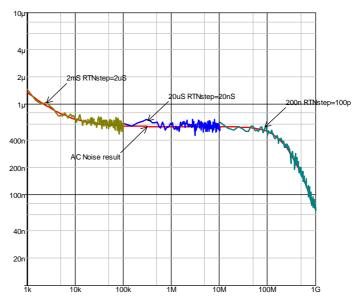

| Real Time Noise Analysis                      |     |

| NEAL THRE INDISE ALIAIVSIS                    | 20/ |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 270271272273273273278279280  mance282282                             |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------|

| Specifying a Single Step Monte Carlo Sweep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 271272273273273278279280  mance282282                                |           |

| Log File       272         Seeding the Random Number Generator       273         Specifying Tolerances       273         Overview       273         Distribution Functions       278         Hspice Distribution Functions       278         TOL, MATCH and LOT Device Parameters       279         Tolerance Models       280         Chapter 8         Convergence, Accuracy and Performance         Overview       282         DC Operating Point       282         Overview       282         Source and GMIN Stepping       283         Pseudo Transient Analysis       284         Junction Initialised Iteration       286         Using Nodesets       286         Transient Analysis       287         What Causes Non-convergence?       287         Fixes for Transient Non-convergence       287         DC Sweep       288 | 272<br>273<br>273<br>273<br>278<br>279<br>280<br>mance<br>282<br>282 |           |

| Seeding the Random Number Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 273<br>273<br>273<br>273<br>278<br>279<br>280<br>mance<br>282<br>282 |           |

| Specifying Tolerances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 273<br>273<br>273<br>278<br>279<br>280<br>mance<br>282<br>282        |           |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 273<br>273<br>278<br>279<br>280<br>mance<br>282<br>282               |           |

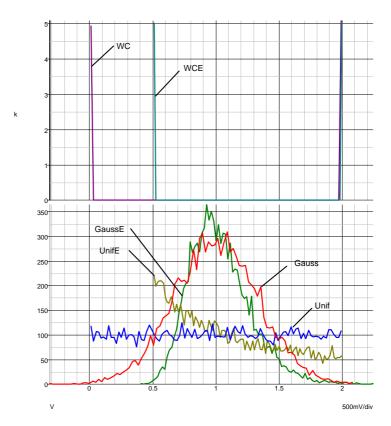

| Distribution Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 273<br>278<br>279<br>280<br>mance<br>282<br>282                      |           |

| Hspice Distribution Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 278<br>279<br>280<br><b>nance</b><br>282<br>282                      |           |

| TOL, MATCH and LOT Device Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 279<br>280<br><b>mance</b><br>282<br>282                             |           |

| Chapter 8         Convergence, Accuracy and Performance           Overview         282           DC Operating Point         282           Overview         282           Source and GMIN Stepping         283           Pseudo Transient Analysis         284           Junction Initialised Iteration         286           Using Nodesets         286           Transient Analysis         287           What Causes Non-convergence?         287           Fixes for Transient Non-convergence         287           DC Sweep         288                                                                                                                                                                                                                                                                                            | 280<br><b>nance</b><br>282<br>282                                    |           |

| Chapter 8         Convergence, Accuracy and Performance           Overview         282           DC Operating Point         282           Overview         282           Source and GMIN Stepping         283           Pseudo Transient Analysis         284           Junction Initialised Iteration         286           Using Nodesets         286           Transient Analysis         287           What Causes Non-convergence?         287           Fixes for Transient Non-convergence         287           DC Sweep         288                                                                                                                                                                                                                                                                                            | 280<br><b>nance</b><br>282<br>282                                    |           |

| Overview         282           DC Operating Point         282           Overview         282           Source and GMIN Stepping         283           Pseudo Transient Analysis         284           Junction Initialised Iteration         286           Using Nodesets         286           Transient Analysis         287           What Causes Non-convergence?         287           Fixes for Transient Non-convergence         287           DC Sweep         288                                                                                                                                                                                                                                                                                                                                                              | 282<br>282                                                           |           |

| Overview         282           DC Operating Point         282           Overview         282           Source and GMIN Stepping         283           Pseudo Transient Analysis         284           Junction Initialised Iteration         286           Using Nodesets         286           Transient Analysis         287           What Causes Non-convergence?         287           Fixes for Transient Non-convergence         287           DC Sweep         288                                                                                                                                                                                                                                                                                                                                                              | 282<br>282                                                           | Chapter 8 |

| DC Operating Point       282         Overview       282         Source and GMIN Stepping       283         Pseudo Transient Analysis       284         Junction Initialised Iteration       286         Using Nodesets       286         Transient Analysis       287         What Causes Non-convergence?       287         Fixes for Transient Non-convergence       287         DC Sweep       288                                                                                                                                                                                                                                                                                                                                                                                                                                   | 282                                                                  | •         |

| Overview         282           Source and GMIN Stepping         283           Pseudo Transient Analysis         284           Junction Initialised Iteration         286           Using Nodesets         286           Transient Analysis         287           What Causes Non-convergence?         287           Fixes for Transient Non-convergence         287           DC Sweep         288                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |           |

| Source and GMIN Stepping       283         Pseudo Transient Analysis       284         Junction Initialised Iteration       286         Using Nodesets       286         Transient Analysis       287         What Causes Non-convergence?       287         Fixes for Transient Non-convergence       287         DC Sweep       288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 202                                                                  |           |

| Pseudo Transient Analysis       284         Junction Initialised Iteration       286         Using Nodesets       286         Transient Analysis       287         What Causes Non-convergence?       287         Fixes for Transient Non-convergence       287         DC Sweep       288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |           |

| Junction Initialised Iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |           |

| Using Nodesets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |           |

| Transient Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |           |

| What Causes Non-convergence?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |           |

| Fixes for Transient Non-convergence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |           |

| DC Sweep288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |           |

| DC Operating Fullit Algorithms200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |           |

| Junction Initialised Iteration289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |           |

| Source Stepping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |           |

| Diagonal GMIN Stepping289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |           |

| Junction GMIN Stepping299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |           |

| Pseudo Transient Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |           |

| Controlling DC Method Sequence291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |           |

| Singular Matrix Errors291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |           |

| Transient Analysis - 'Time step too small' Error291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |           |

| Accuracy and Integration Methods29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |           |

| A Simple Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |           |

| Iteration Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |           |

| Time Step Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ∠ყა                                                                  |           |

| Accuracy of AC analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 205                                                                  |           |

| Summary of Tolerance Options295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |           |

| Integration Methods - METHOD option296                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 295                                                                  |           |

|           | Single Step Runs                                  | 298   |

|-----------|---------------------------------------------------|-------|

|           | Using Multiple Cores for Single Step Runs         | 298   |

|           | Multi-core Multi-step Simulation                  | 299   |

|           | Matrix Solver                                     | 299   |

|           |                                                   |       |

| Chapter 9 | Digital Simulation                                |       |

|           | Overview                                          | 300   |

|           | Logic States                                      | 300   |

|           | State resolution table                            | 301   |

|           | Analog to Digital Interfaces                      | 301   |

|           | How A-D Bridges are Selected                      | 303   |

|           | Logic Families                                    | 303   |

|           | Logic Family Model Parameters                     | 304   |

|           | Logic Compatibility Tables                        | 304   |

|           | Logic Compatibility File Format                   | 305   |

|           | Supported Logic Families                          | 306   |

|           | Universal Logic Family                            | 307   |

|           | Internal Tables                                   | 307   |

|           | Load Delay                                        | 307   |

|           | Overview                                          | 307   |

|           | Output Resistance                                 | 307   |

|           | Input Delay                                       | 307   |

|           | Wire Delay                                        | 308   |

|           | Digital Model Libraries                           | 308   |

|           | Using Third Party Libraries                       | 308   |

|           | Arbitrary Logic Block - User Defined Models       | 308   |

|           | Overview                                          | 308   |

|           | An Example                                        | 308   |

|           | Example 2 - A Simple Multiplier                   |       |

|           | Example 3 - A ROM Lookup Table                    | 311   |

|           | Example 4 - D Type Flip Flop                      | 312   |

|           | Device Definition - Netlist Entry & .MODEL Parame | eters |

|           | 312                                               |       |

|           | Language Definition - Overview                    | 314   |

|           | Language Definition - Constants and Names         | 314   |

|           | Language Definition - Ports                       | 314   |

|           | Language Definition - Registers and Variables     | 316   |

|           | Language Definition - Assignments                 | 319   |

|           | Language Definition - User and Device Values      | 322   |

|           | Diagnostics: Trace File                           | 322   |

|           | Mixed-mode Simulator - How it Works               | 323   |

|           | Event Driven Digital Simulator                    | 323   |

|           | Interfacing to the Analog Simulator               |       |

| - | _                     |   |        |     | • | $\overline{}$ |          |      |     |     |

|---|-----------------------|---|--------|-----|---|---------------|----------|------|-----|-----|

| 1 | $\sim$                | n | $\sim$ | 1   |   | ٠,            | $\neg r$ | nte. | n   | ·+c |

| 1 | $\boldsymbol{\sigma}$ | u |        | ()I | • | (             | "        | 116  | : 1 | 1.  |

| Enhancements over XSPICE3 | 324 |

|---------------------------|-----|

|---------------------------|-----|

# **Chapter 1 Introduction**

### Overview

This manual provides full reference documentation for the SIMetrix simulator. Essentially the simulator receives a netlist as its input and creates a binary data file and list file as its output. The netlist defines the circuit topology and also specifies the analyses to be performed by the simulator. The netlist may directly include any device models required or these may be automatically imported from a device model library.

The simulator may be operated in GUI mode or non-GUI mode. GUI mode is the normal method of operation and requires the SIMetrix front end. In non-GUI mode the simulator runs stand alone in a non-interactive fashion and may be set to run at low priority in the background.

### The SIMetrix Simulator - What is it?

The SIMetrix simulator core comprises a direct matrix analog simulator closely coupled with an event driven gate-level digital simulator. This combination is often described as *mixed-mode* or *mixed-signal* and has the ability to efficiently simulate both analog and digital circuits together.

The core algorithms employed by the SIMetrix analog simulator are based on the SPICE program developed by the CAD/IC group at the department of Electrical Engineering and Computer Sciences, University of California at Berkeley. The digital event driven simulator is derived from XSPICE developed by the Computer Science and Information Technology Laboratory, Georgia Tech. Research Institute, Georgia Institute of Technology.

### What is in This Manual

This reference manual contains detailed descriptions of all simulator analysis modes and supported devices.

# **Chapter 2 Running the Simulator**

# Using the Simulator with the SIMetrix Schematic Editor

Full documentation on using the SIMetrix schematic editor for simulation is described in the SIMetrix User's manual. However, just a few features of the schematic editor are of particular importance for running the simulator and for convenience their description is repeated here.

### Adding Extra Netlist Lines

The analysis mode selected using the schematic editor's Simulator | Choose Analysis... menu is stored in text form in the schematic's simulator command window. If you wish, it is possible to edit this directly. Sometimes this is quicker and easier than using the GUI especially for users who are familiar with the command syntax.

Note that the text entered in the simulator command window and the Choose Analysis dialog settings remain synchronised so you can freely switch between the two methods.

To open the simulator command window, select the schematic then press the F11 key. It has a toggle action, pressing it again will hide it. If you have already selected an analysis mode using the Choose Analysis dialog, you will see the simulator statements already present.

The window has a popup menu selected with the right key. The top item **Edit file at cursor** will open a text editor with the file name pointed to by the cursor or selected text item if there is one.

The simulator command window can be resized using the splitter bar between it and the schematic drawing area.

You can add anything you like to this window not just simulator commands. The contents are simply appended to the netlist before being presented to the simulator. So, you can place .PARAM statements, device models, inductor coupling specifications, .OPTION statements or simply comments. The Choose Analysis dialog will parse and possibly modify analysis statements and some .OPTIONS settings but will leave everything else intact.

# **Displaying Net and Pin Names**

It is sometimes necessary to know the name used for a particular net on the schematic to be referenced in a simulator statement (such as .NOISE) or for an arbitrary source input. There are two approaches:

Find out the default name generated by the schematic editor's netlist generator.

To do this, move the mouse cursor over the net of interest then observe the netname in the status bar in the form "NET=???".

Force a net name of your choice. For this, use a terminal or small terminal symbol. These can be found under the Place | Connectors menu. After placing on the schematic, select it then press F7 to edit its name. This name will be used to name the net to which it is connected.

### **Editing Device Parameters**

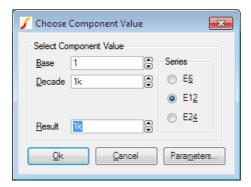

To use any of the additional parameters in a schematic, use the Parameters button in the dialog box opened by F7 or the equivalent menu. For example you see this box when editing a resistor

Pressing the Parameters button will open another dialog from which you can edit parameter values:

You can also bring up this box directly using the right click menu **Edit Additional Parameters...**

### **Editing Literal Values - Using shift-F7**

The above method is not infallible as it requires the schematic editor to know about the device being edited. In some circumstances, this will require special properties to be present on the symbol and these may have not been defined. (for example something to tell the schematic what level a MOSFET is)

Another situation where the usual device editing methods may be unsuitable is when you need to define a parameter as an expression.

In these situations you can use shift-F7. This will edit the device's literal value including any model names exactly as it will be placed in the netlist. shift-F7 bypasses all smart algorithms and presents you with the raw values and you must also supply raw values. For example, here is what you might enter for a MOSFET referencing a model called N1

```

N1 L={LL-2*EDGE} W=\{WW-2*EDGE\}

```

Note the model name must be included.

# **Running in non-GUI Mode**

### Overview

The simulator can be run in a non-interactive non-GUI mode independently of the front end. This is useful for running simulation 'batches' controlled by a proprietary script or batch language such as shell scripts or DOS batch files.

Under Linux this allows a simulation to be run without an X-server.

Under Windows, the simulator will run as a 'console mode' application and no GUI elements will be created.

When run in this mode, the simulator will read in the specified netlist, run the simulation then close and return control to the calling program. It will generate a binary data file and a list file.

# **Important Licensing Information**

Non-GUI mode is only possible if you are using network licensing. This feature is not available if you are using a portable (i.e. dongled) license. Please contact support if you have a non-network license and wish to use non-GUI simulation mode.

This mode of operation is 'counted' for licensing purposes. This means you can only run one non-GUI simulation process for each license issued even if all are run by a single user on a single machine. By contrast, regular simulation initiated *manually* through the GUI are not counted and any number of runs may be initiated on the same machine by the same user for this purpose.

These restrictions have been made to limit exploitation of multiple core machines for simulations run from non-SIMetrix environments.

### **Syntax**

The command syntax is as follows:

SIM [/config "config\_location"] [/gui mode] [/check]

[/an "analysis\_line"] [/list list\_filename] [/options "options"] [/nolist]

[/lowPriority] [/nodata] [/k] [/extraline extra\_line] netlist\_file

[data\_file]

config\_location

Location of file holding configuration settings. Configuration settings include global options and global model library locations. The value must be of the form:

PATH;pathname

pathname may use system symbolic path values such as %EXEPATH%. See *User's Manual* for details.

If not specified, the configuration settings will be taken from the Base.sxprj file. See the *User's Manual* for details on where this file is located

Alternatively, you can specify the location using a setting in the startup.ini file. Add a value called SimConfig to the [Startup] section and give it a value of:

PATH;pathname

The startup.ini file must be located in the same directory as the SIMetrix executable binary. (SIMetrix.exe on Windows, SIMetrix on Linux). See the *User's Manual* for more information on the startup.ini file.

Note that the /config switch if present must always appear before the first argument to the command.

mode

Mode of operation. Default = -1. Valid values are -1, 0, 1 and 2 but only -1 and 1 are meaningful for stand-alone operation. 0 and 2 are used when starting the simulator process from the front end. -1 (same as omitting /gui) runs the simulator in console mode with all messages output to the console or terminal window. 1 enables GUI mode where the simulator runs in a stand-alone mode but displays a graphical status box showing messages and simulator progress. This mode is used by the 'asynchronous' menus in the front end.

analysis\_line

If /an switch is specified, *analysis\_line* specifies the analysis to be performed and overrides all analysis lines specified in the netlist

list\_filename

Name of list file. Default is main netlist file name with extension .OUT. Enclose path name in quotes if it contains spaces.

### Chapter 2 Running the Simulator

options List of options valid for .OPTIONS statement.

netlist\_file File name of netlist.

data\_file File to receive binary data output.

/check If specified, the netlist will be read in and parsed but no

simulation will be run. Used to check syntax

/nolist If specified, no list file will be created

/lowPriority If specified, the simulator will be run as a low priority process,

i.e. in the background. Recommended for long runs.

/nodata Only vectors explicitly specified using .KEEP or .PRINT will

be output to the binary file. Equivalent to '.KEEP /nov /noi

/nodig' in the netlist.

/k If specified, the program will not finally terminate until the user

has pressed enter and a message to that effect will be displayed. Under Windows, if the program is not called from the DOS prompt but from another program, a console will be created for receiving messages. The console will close when the program exits sometimes before the user has had a chance to read the messages. This switch delays the exit of the program and hence

the destruction of the console.

extra\_line An additional line that will be appended to the netlist. This

permits simple customisation of the netlist. This should be enclosed in double quotation marks if the line has spaces.

### **Aborting**

Press cntrl-C - you will be asked to confirm. The simulation will be paused while waiting for your response and will continue if you enter 'No'. This is an effective means of pausing the run if you need CPU cycles for another task, or you wish to copy the data file. See "Reading Data" below.

# Reading Data

A data file will be created for the simulation results as normal (see "The Binary Data File" on page 25). You can read this file after the simulation is complete use the SIMetrix menu File | Load Data... You may also read this data file while the simulation is running but you must pause the simulation first using cntrl-C.

Important: if you read the data file before the simulation is complete or aborted, the file entries that provide the size of each vector will not have been filled. This means that the waveform viewer will have to scan the whole file in order to establish the size of the vectors. This could take a considerable time if the data file is large.

# **Configuration Settings**

Configuration settings consist of a number of persistent global options as well as the locations for installed model libraries.

When the simulator is run in GUI mode, its configuration settings are controlled by the front end and stored wherever the front end's settings are stored. See the *User's Manual* for more details.

The settings when run in non-GUI mode are stored in a configuration file which in fact defaults to the same location as the default location for the front end's settings. You can change this location using the /config switch detailed above (page 15)

The format of the configuration file is:

[Options] option\_settings

[Models] model\_libraries

Where:

option\_settings

These are of the form *name=value* and specify a number of global settings. Boolean values are of the form *name=* without a value. If the entry is present it is TRUE if absent it is FALSE. Available global settings are detailed below.

model libraries

A list of entries specifying search locations for model libraries. These are of the form name=value where name is a string and value is a search location. The string used for name is arbitrary but must be unique. Entries are sorted alphabetically according to the name and used to determine the search order. value is a path name and may contain wildcards (i.e. '\* and '?')

### **Global Settings**

| Name                  | Туре    | Default          | Description                                                                                                                                                                          |

|-----------------------|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NoStopOnUnknownParam  | String  | WARN             | Specifies action to be taken in the event of an unknown parameter being encountered in a .MODEL statement. Choices are:                                                              |

|                       |         |                  | TRUE: No action taken, simulation continues normally FALSE: An error will be raised and the simulation will abort WARN: A warning will be displayed but the simulation will continue |

|                       |         |                  | This will be overridden<br>by a .OPTIONS setting<br>of the same name. See<br>page 245                                                                                                |

| MaxVectorBufferSize   | Numeric | 32760            | See "Data Buffering" below                                                                                                                                                           |

| TotalVectorBufferSize | Numeric | Available RAM/10 | See "Data Buffering" below                                                                                                                                                           |

| TempDataDir           | String  | %STARTDIR%       | Location of temporary<br>binary data file if<br>data_file is not<br>specified on command<br>line                                                                                     |

| LibraryDiagnostics    | String  | Full             | Controls output of<br>messages relating to<br>model library search.<br>Specify None to<br>disable                                                                                    |

### **Data Buffering**

The simulator buffers data before writing it to disk. By doing so the binary data file can be organised more efficiently allowing data to be recovered from it quickly. There is a relationship between buffer size and read in time as illustrated by the following table. This shows the time taken to read in a 14MByte vector from a 1GByte data file with the system disk cache cleared. The tests were performed with three different buffer sizes on two different systems. One system was an old notebook computer with an IDE disk system. The other was a machine with a high performance SCSI Ultra 320 disk.

| System    | Buffer size     | Read time |

|-----------|-----------------|-----------|

| IDE       | 32768 (default) | 8.1 secs  |

|           | 250K            | 3.1 secs  |

|           | 1 Meg           | 2.8 secs  |

| Ultra 320 | 32768 (default) | 4.1 secs  |

|           | 250K            | 0.75 secs |

|           | 1Meg            | 0.23 secs |

Note that the buffer size referred to in the above table is for each vector.

By default, the simulator won't allocate more than 10% of your system RAM to vector buffers. Clearly if you are running a large circuit and saving many vectors, the buffer sizes could reduce to levels that would make data retrieval very slow. In this case you may wish to consider increasing the memory that is allowed for these buffers. Two configuration settings control the vector buffering. These are:

- MaxVectorBufferSize. This sets the maximum size that will be used for any

individual vector. The default is 32768 bytes. If you have a high performance

SCSI disk system, you may benefit from increasing this value

- TotalVectorBufferSize. This sets the maximum amount of memory in bytes used for all buffers. It defaults to a value equal to 10% of your system RAM. This is usually sufficient for most applications but if you are simulating a very large circuit and have sufficient RAM you may like to increase this value

The disk will not be written to until the buffers are full. With an all analog circuit all the buffers reach their full state at the same time so they all get written to disk at the same time. If you have 2G of RAM and are simulating a large circuit, approximately 200M of data will be written to the disk at regular intervals. This will result in a pause in the simulation coupled with a great deal of disk activity.

Note that both MaxVectorBufferSize and TotalVectorBufferSize may be set from the front end using the Set command. See the *User's Manual* for details.

# **Netlist Format**

The SIMetrix netlist format follows the general format used for all SPICE and SPICE compatible simulators. However, with so many SPICE derivatives and with two significantly different versions of SPICE itself (SPICE 2 and SPICE 3) it is not possible to define a standard SPICE format. SIMetrix has been developed to be as compatible as possible with model libraries that can be obtained from external sources. For discrete devices, models are usually SPICE 2 compatible but some use extensions originally developed for PSpice®. IC designers usually receive model files from fabrication companies and these are available for a variety of simulators usually including Hspice®. SIMetrix is compatible with all of these but simultaneous compatibility with all formats is not technically possible due to a small number of syntax details - such as the character used for in line comments. To overcome these

minor difficulties, a language declaration can be placed at the top of the netlist and any file included using .INC (page 222) or the Hspice® variant of .LIB (page 227). This is described in the following sections.

#### File Format

A complete netlist consists of:

- A title line

- Optional language declaration

- Device lines

- Statement lines

- Comment lines

The title line must be the first line of the file and may be empty. The remaining lines - with some exceptions - may be placed in any order

All other lines are defined by their first non-whitespace character as follows.

- · Statement lines begin with a period: '.'

- Comment lines begin with an asterix: '\*'