IBM Systems and Technology Group

# Designing low-frequency decoupling using SIMPLIS

K. Covi

© 2007 IBM Corporation

## Traditional approach to sizing decoupling

- Determine effective ESR required

- ► Parallel electrolytic caps until ESR =  $\Delta V / \Delta I$

- where  $\Delta V$  = desired voltage tolerance

$\Delta I$  = worst-case load change

- □ Example: p690 Power 4 CPU

- ►  $\Delta V = 3\%$  of 1.5V,  $\Delta I = 1500A \rightarrow$  effective ESR =  $30u\Omega$

- 2 capacitor books with over 800 1000uF aluminum electrolytic caps

- CPU decoupling

- 383 1000uF 38m $\Omega$  aluminum electrolytics per cap book  $\rightarrow$  50u $\Omega$

- 240 470uF 25m $\Omega$  organic Tantalum on processor board  $\rightarrow$  104u $\Omega$

- Effective ESR =  $33.8u\Omega$  max, typically much less

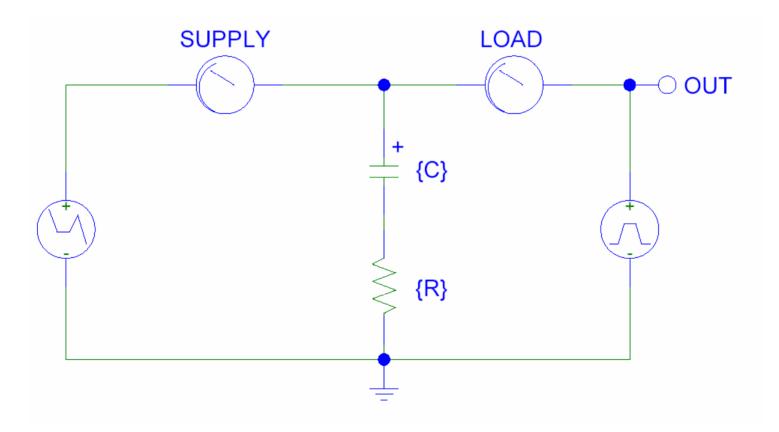

#### Simplified decoupling model

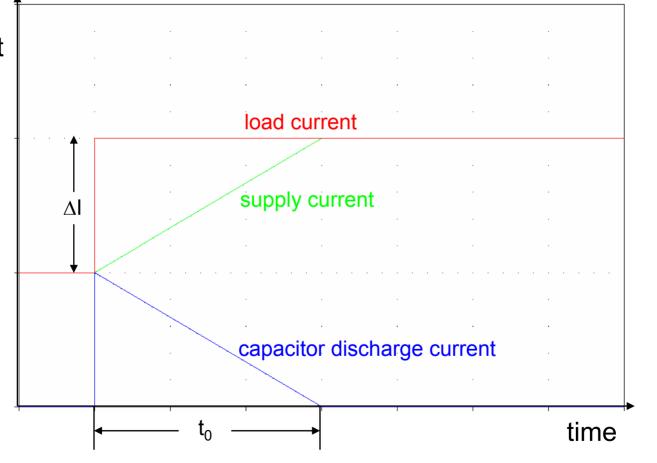

#### Current supplied by capacitor after a load step

current

#### Solve for maximum $\Delta V$

For  $t_0 \le \tau$ :  $\Delta V = \Delta I \bullet R$

For  $t_0 > \tau$ :

$$\Delta \mathsf{V} = \Delta \mathsf{I} \bullet (\mathsf{R}/2) \bullet (\tau/t_0 + t_0/\tau)$$

( $\tau$  = RC = capacitor time constant)

#### Response is limited by ESR!

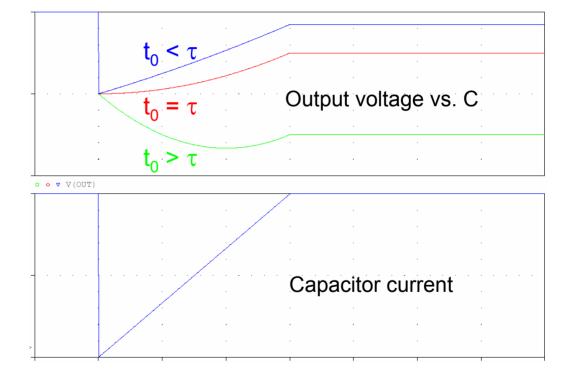

#### But it's not so simple anymore

- Denser packaging limits the number of output caps

- Fewer caps with much lower ESR  $\rightarrow$  shorter time constant

- > All multi-layer ceramic designs  $\rightarrow$  very short time constant

- $\Box$  Result is that ESR no longer predicts  $\Delta V$

- ► Regulator response time typically longer than RC time constant of decoupling caps ( $t_0 > \tau$ )

- □ Can use  $\Delta V = \Delta I \cdot (R/2) \cdot (\tau/t_0 + t_0/\tau)$  equation, but how to determine  $t_0$ ?

- t<sub>0</sub> usually limited by feedback compensation

## **Computer modeling**

#### SPICE

Different models for transient and AC analysis

- Full switching model is very slow

- Convergence problems!!!

SIMPLIS

- Same model use for both transient and AC analysis

- ► Up to 50x faster than SPICE simulators

- No convergence problems

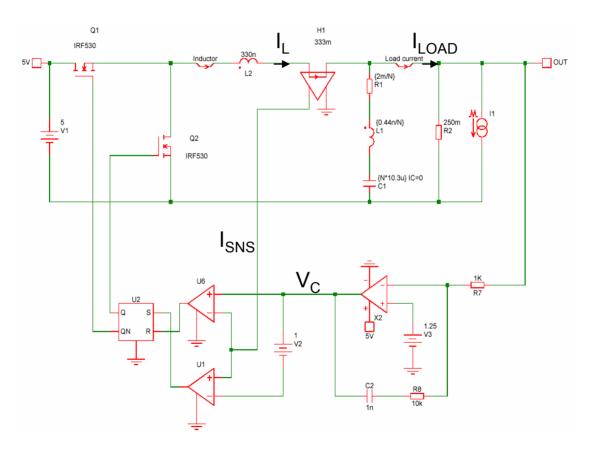

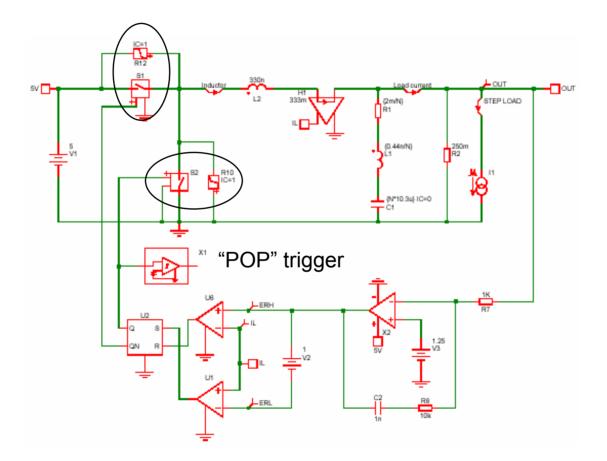

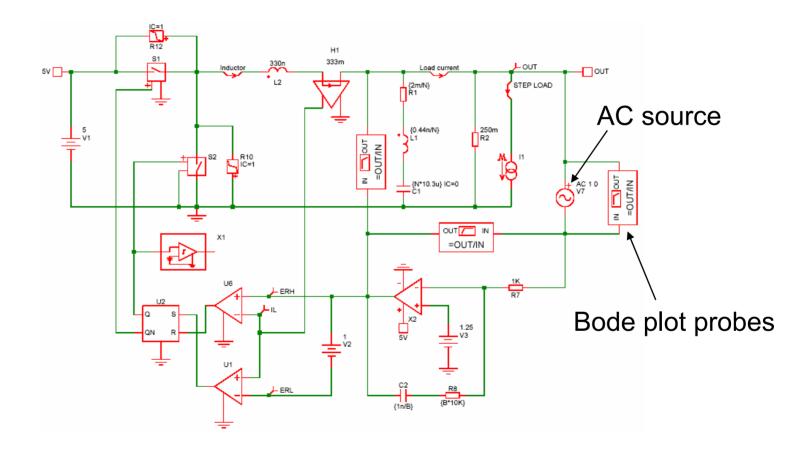

#### **Current-Mode Hysteretic Buck Converter**

Switching frequency ~800kHz

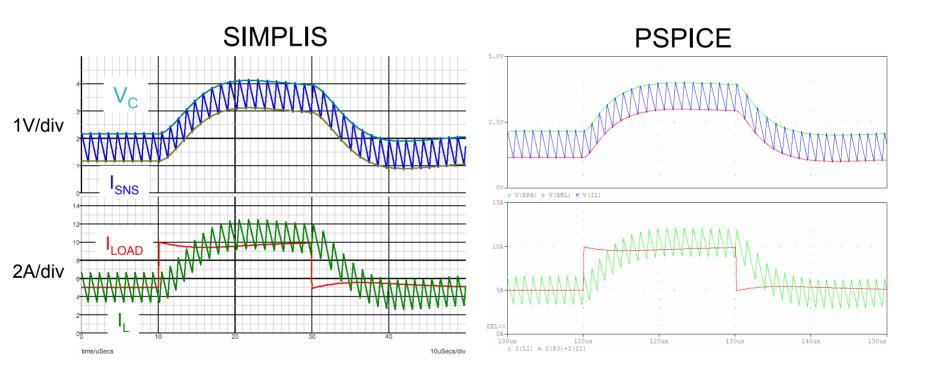

## Key waveforms

#### Transient response virtually identical

18 October 2007

## AC analysis with SIMPLIS

| <br>  | _ | _ |   |

|-------|---|---|---|

|       |   |   | _ |

|       | _ | _ | _ |

|       | _ |   | _ |

| _     | _ | _ | _ |

| <br>_ | _ | _ | _ |

| <br>  | _ | _ |   |

#### SIMPLIS model

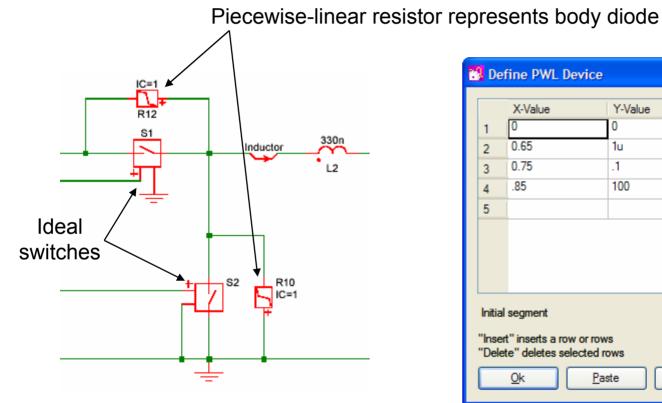

#### MOSFETs replaced by ideal switch model

| 2 | De     | fine PWL Device                                            |                     |

|---|--------|------------------------------------------------------------|---------------------|

|   |        | X-Value                                                    | Y-Value             |

|   | 1      | 0                                                          | 0                   |

|   | 2      | 0.65                                                       | 1u                  |

|   | 3      | 0.75                                                       | .1                  |

|   | 4      | .85                                                        | 100                 |

|   | 5      |                                                            |                     |

|   |        |                                                            |                     |

|   | "Inser | segment<br>t" inserts a row or rov<br>te" deletes selected |                     |

|   |        |                                                            | aste <u>C</u> ancel |

These simplifications have no effect on regulator dynamic performance

## What does "POP" mean?

#### POP stands for Periodic Operating Point Analysis

- POP analysis rapidly locates the steady state operating point of a switching system without having to simulate the startup transient conditions. This considerably speeds the study of effects such as load transients.

- Unlike the static methods used in SPICE, this analysis mode emulates a frequency sweep measurement as might be conducted on real hardware producing gain and phase plots without having to derive averaged models.

(excerpted from http://www.transim.com/SS\_simplis.html)

#### POP algorithm finding periodic steady state

14

#### Add AC source to measure loop gain

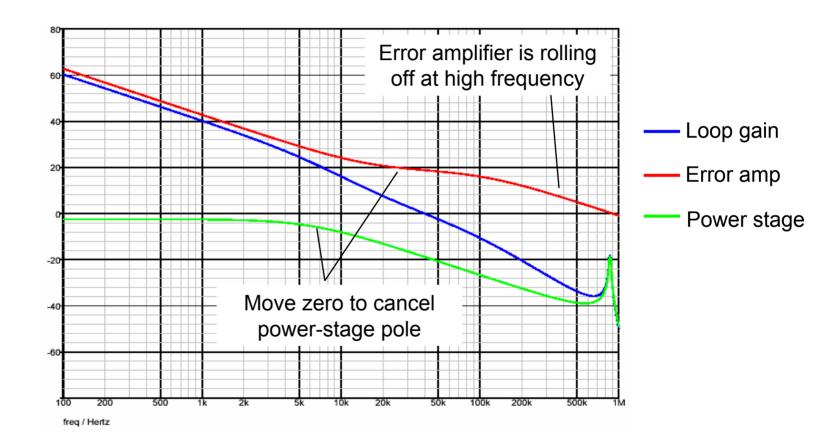

#### Loop gain

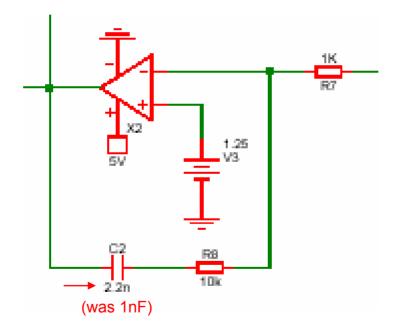

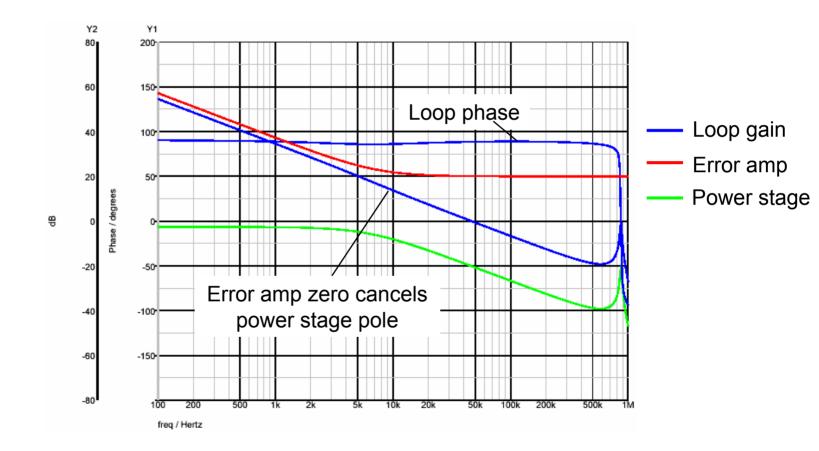

#### Move zero to match power stage

Zero moves from 15.9kHz to 7.2kHz

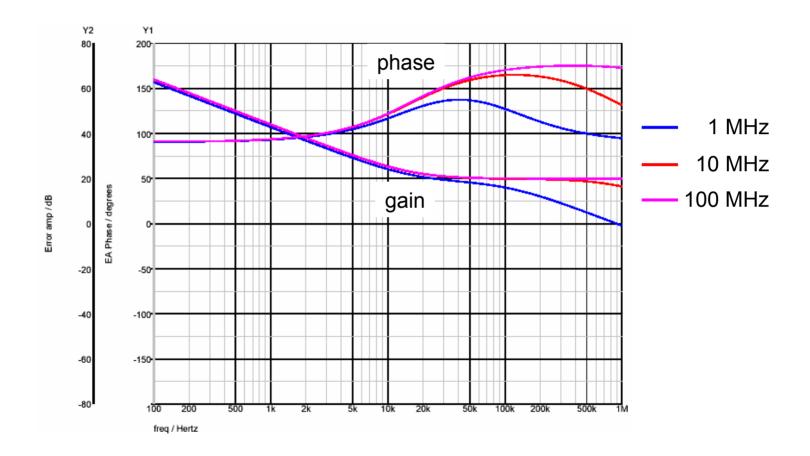

#### Compensator gain and phase vs op amp GBW

#### Updated Loop gain

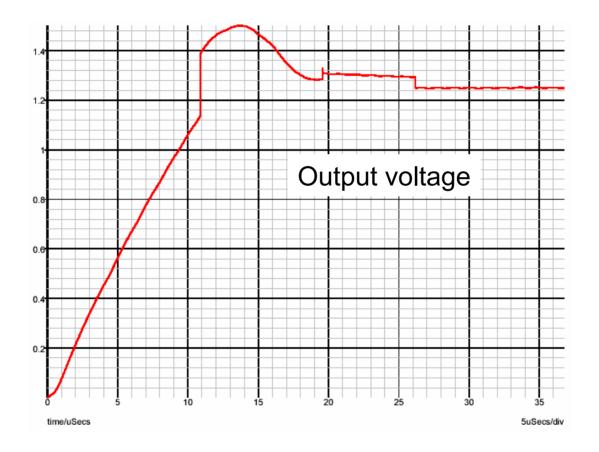

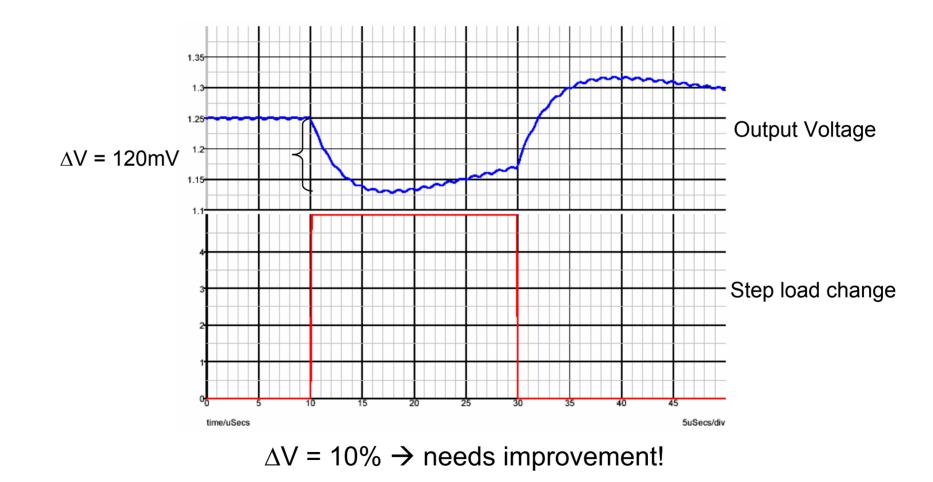

#### Step response

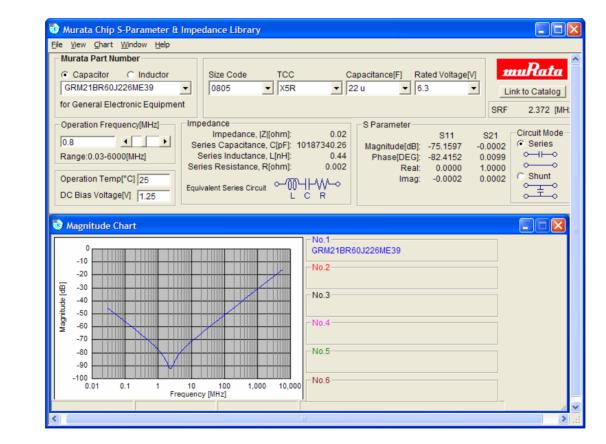

## 22uF 0805 X5R decoupling cap model:

#### Impedance @ 1.25V & 800kHz

C=10.2uF

$R=2m\Omega$

L=0.44nH

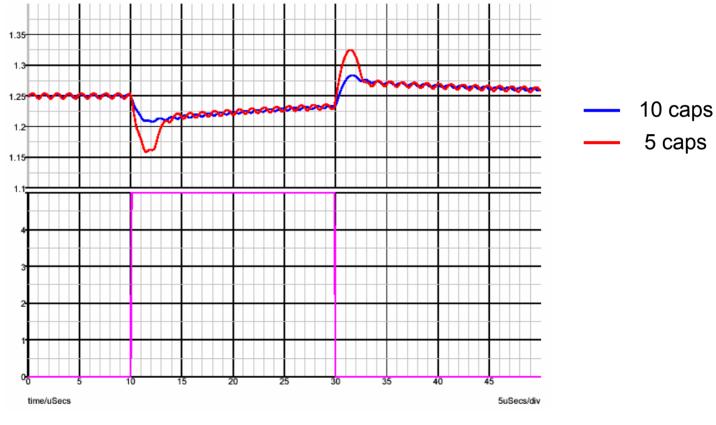

#### Step response with 10 caps

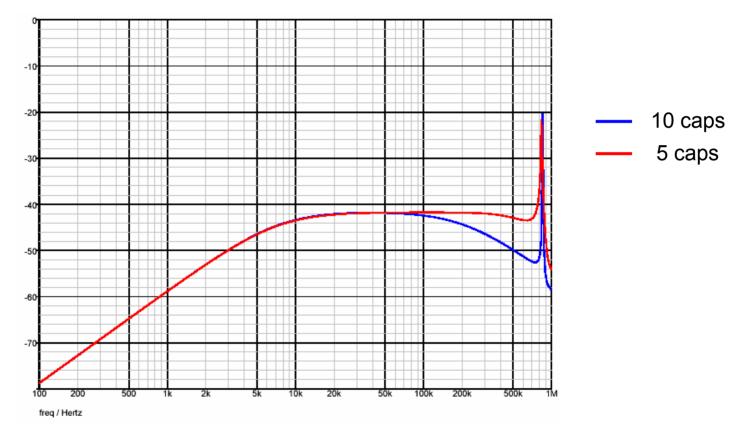

## **Output impedance**

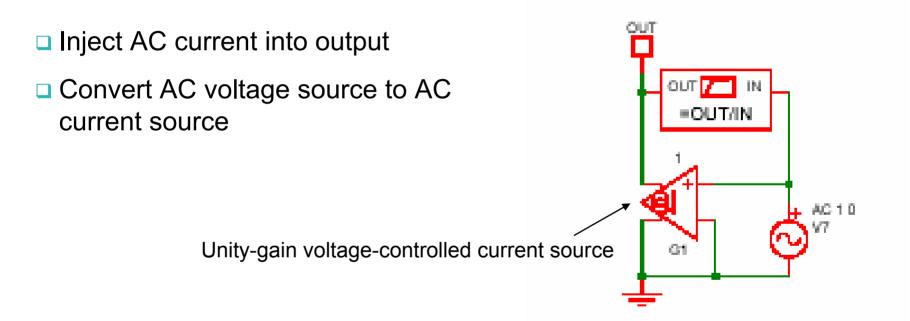

#### Measuring output impedance

#### Open- and closed-loop output impedance

25

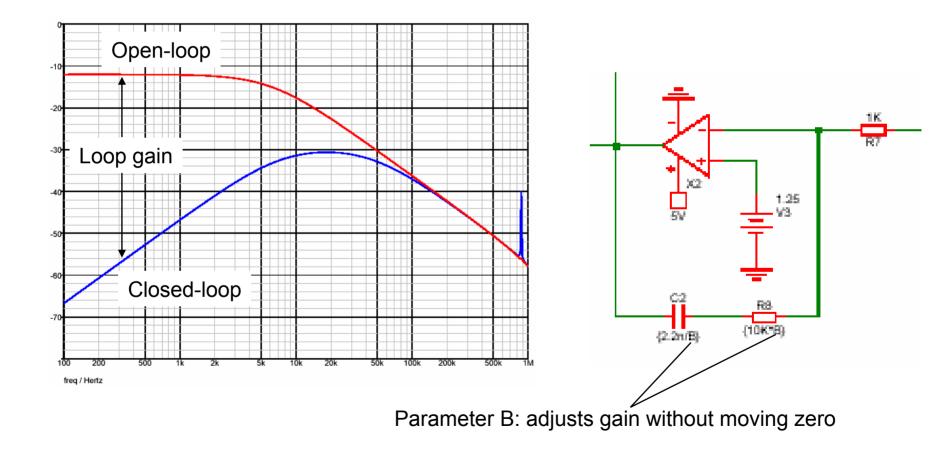

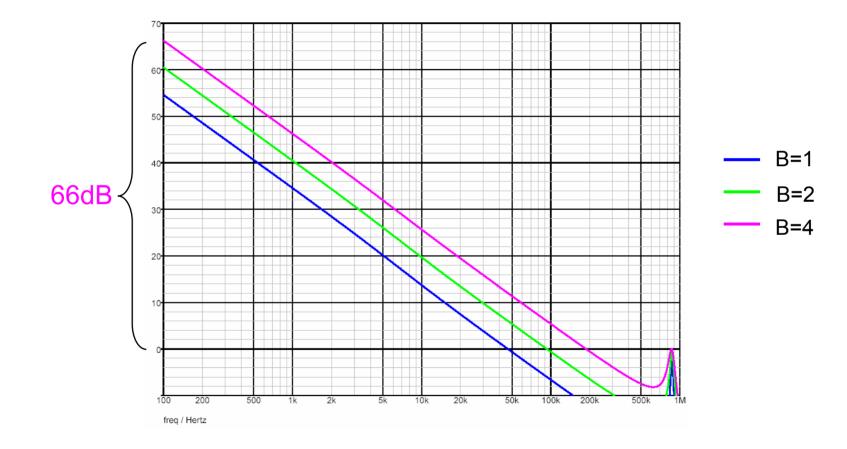

#### Loop gain vs B

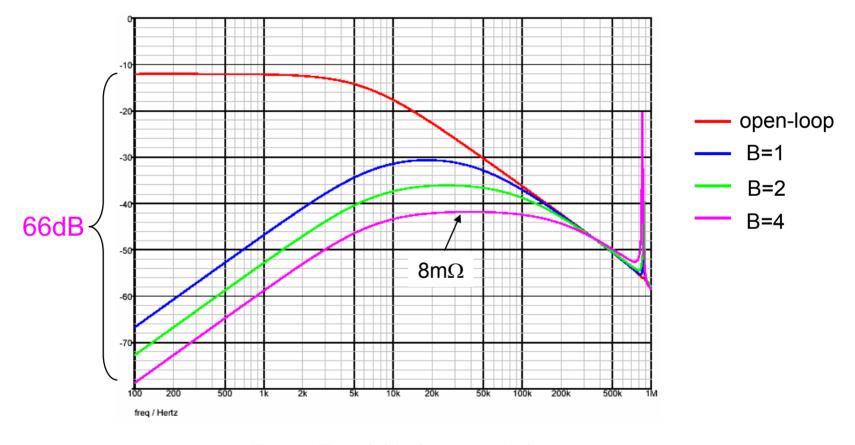

#### Output impedance vs loop gain

#### $Z_{CL} = Z_{OL} / (1 + loop gain)$

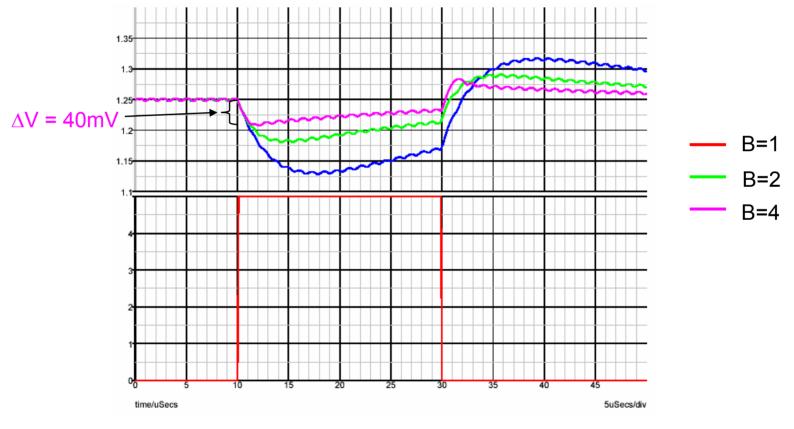

#### Step response vs loop gain

#### $8m\Omega \times 5A = 40mV \rightarrow$ excellent agreement!

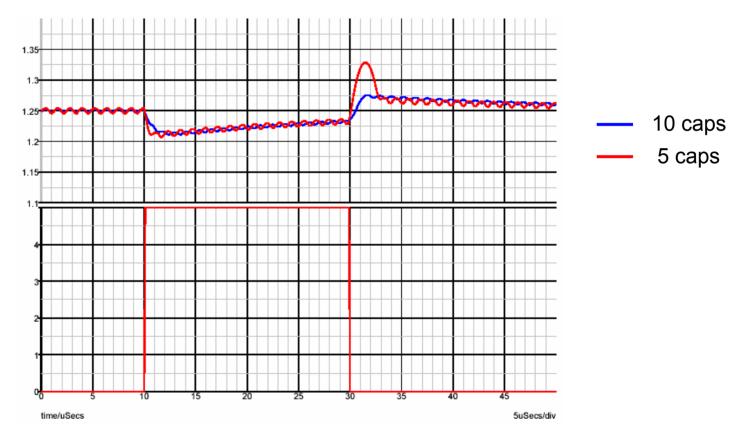

#### Can the number of output caps be reduced?

Peak output impedance the same with 5 or 10 caps

#### Step response vs number of output caps

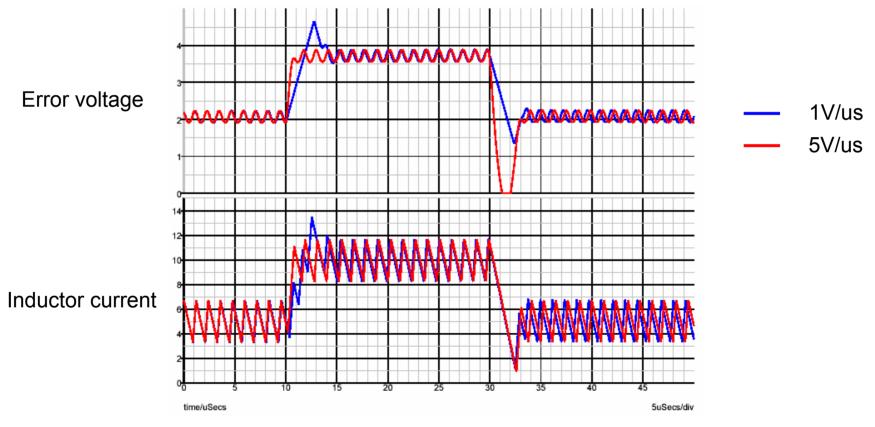

#### What's causing the overshoot?

#### Slew rate limiting of error amp!

Transient response was limited by 1V/us max slew rate

#### Parameterized op amp

| Model Level                        | 2      | Offset Voltage                  | 0    |   | Bias Current                         | 10p    |  |

|------------------------------------|--------|---------------------------------|------|---|--------------------------------------|--------|--|

| Offset Current                     | 1n 🛟   | Open-loop Gain in V/V           | 100k | • | Gain-bandwidth in Hz (Level 2)       | 100Meg |  |

| Pos. Slew Rate in V/s (Level 2)    | 1Meg   | Neg. Slew Rate in V/s (Level 2) | 1Meg | - | CMRR                                 | 100k   |  |

| PSRR                               | 100k 🛟 | Input Resistance                | 1Meg | 1 | Max. Output Source Current (Level 2) | 5m     |  |

| Max. Output Sink Current (Level 2) | 5m 🛟   | Output Resistance               | 100  | 1 | Output AC Resistance                 | 50     |  |

| Power Diss.                        | 1m 🛟   | Headroom Pos. (Level 2)         | 0    | 1 | Headroom Neg. (Level 2)              | 0      |  |

#### I forgot to adjust SR when I increased GBW (again!)

#### Step response with 5V/us amplifier

Power stage cannot slew fast enough in negative direction

#### Summary

34

- Difficult to size decoupling with all ceramic or low-ESR electrolytic caps

- Computer modeling is essential to predict the regulator response to sudden load changes

- SPICE is OK for simulating transient behavior, but AC analysis not possible with switching model

- SIMPLIS provides both transient and AC analysis with the same model

- Relatively easy to size decoupling once loop gain can be observed and the compensation optimized

## Thank you!