back to overview ^

» DVM Test Report: Steady-State|Steady-State|Vin Nominal|20%

| Test Details | |

| Schematic | 4.2_LTC3406B - DVM ADVANCED.sxsch |

| Test | Steady-State|Steady-State|Vin Nominal|20% |

| Date / Time | 4/18/2013 10:58:55 AM |

| Report Directory | DVM_REPORTS\2013-04-18-10_58_35_AM\Steady-State\Steady-State\Vin Nominal\20% |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 88.3966% |

| Efficiency_nom | 88.3966% |

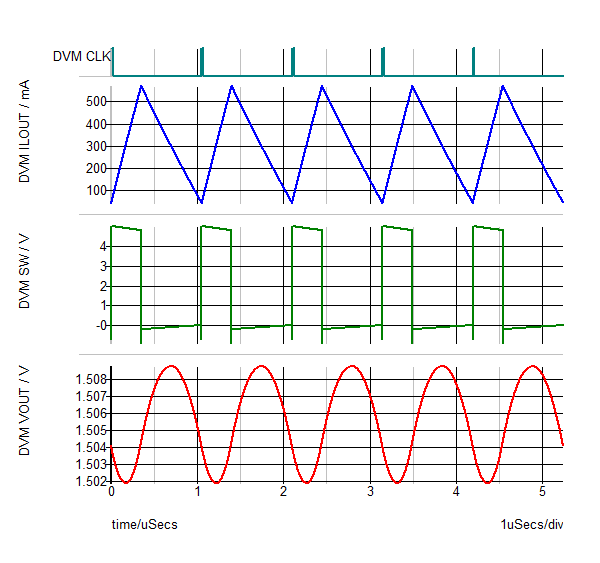

| Frequency(CLK) | 955.66161kHertz |

| Power(LOAD123) | 451.902m |

| Power(SRC) | 511.221m |

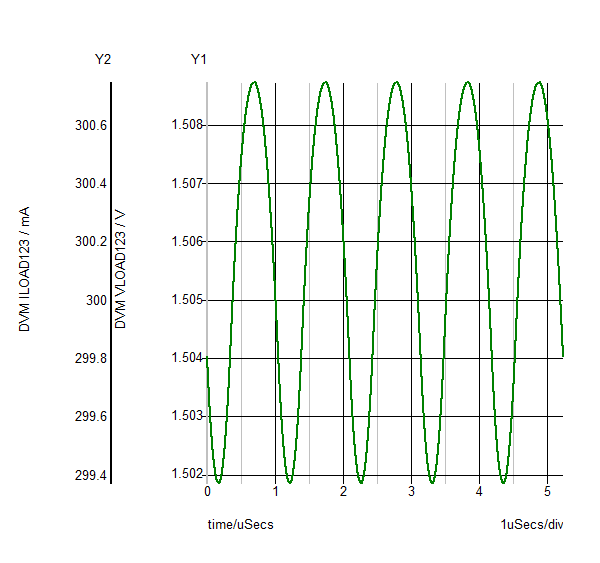

| ILOAD123 | AVG 300.134m MIN 299.37m MAX 300.744m RMS 300.135m |

| ILOUT | AVG 300.134m MIN 40.3027m MAX 567.019m RMS 336.488m |

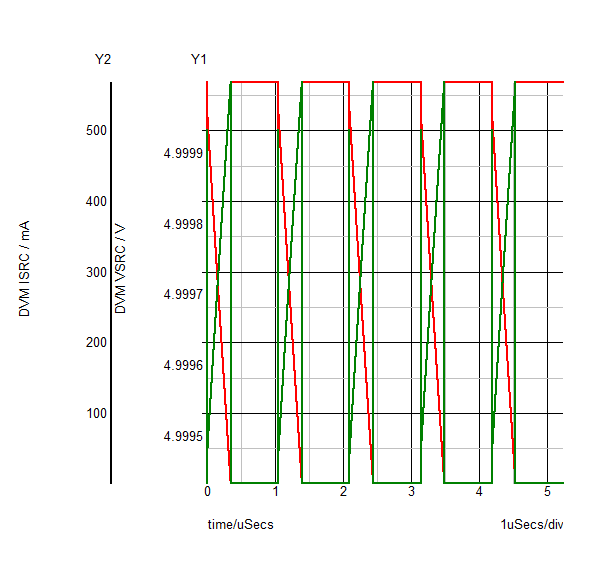

| ISRC | AVG 102.252m MIN 423.264u MAX 567.443m RMS 197.524m |

| SW | AVG 1.53567 MIN -926.805m MAX 4.98365 RMS 2.809 |

| VLOAD123 | AVG 1.50566 MIN 1.50183 MAX 1.50872 RMS 1.50566 PK2PK 6.89408m |

| VOUT | AVG 1.50566 MIN 1.50183 MAX 1.50872 RMS 1.50566 |

| VSRC | AVG 4.9999 MIN 4.99943 MAX 5 RMS 4.9999 |

| Measured Spec Values | |

| Max_VLOAD123 | PASS: Max. Output1 Voltage (1.50872) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD123 | PASS: Min. Output1 Voltage (1.50183) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

LOAD123

VLOAD123

ILOAD123

|

|

| SXGPH File | simplis_pop56_1968.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop56_1958.sxgph |

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop56_1963.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop56_1950.sxgph |