» DVM Test Report Overview

| General | |

| Schematic | 4.2_LTC3406B - DVM ADVANCED.sxsch |

| Testplan | dvm_advanced.testplan |

| Original Testplan Filename | dvm_builtin-efficiency_dcdc_1in_1out.testplan |

| Date / Time | 2013-04-18 10:58:40 AM |

| Report Directory | DVM_REPORTS\2013-04-18-10_58_35_AM |

| Log File | dvm_advanced.log |

| # of Tests Run | 34 of 34 (33 Passed, 1 Skipped) |

| Total Time | 3m 19s |

| Design Specifications | |

| Circuit Name | LTC3406B |

| Description | Synchronous Buck |

| Input 1 | 5.000 V (4.5 V to 5.5 V) |

| Output 1 | 1.505 V (±5%) @ 1.5 A |

| Switching Frequency | 955kHz |

| Excel-compatible Results | |

| Scalar Results | dvm_advanced_table_scalars.txt |

| Spec Results | dvm_advanced_table_specs.txt |

| Overview Graphs | |

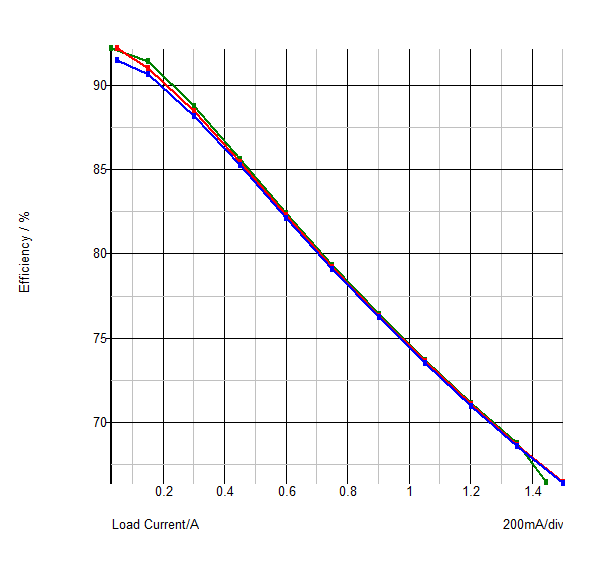

Efficiency

Vin Max

Vin Min

Vin Nom

|

|

| SXGPH File | simplis_pop86_3035.sxgph |

| Source Test | Steady-State|Generate Efficiency Curves |

| Test 1 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|Light Load |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\Light Load\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 2 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|10% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\10%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 3 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|20% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\20%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 4 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|30% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\30%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 5 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|40% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\40%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 6 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|50% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\50%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 7 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|60% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\60%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 8 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|70% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\70%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 9 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|80% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\80%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 10 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|90% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\90%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 11 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Nominal|100% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Nominal\100%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 12 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|Light Load |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\Light Load\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 13 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|10% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\10%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 14 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|20% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\20%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 15 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|30% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\30%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 16 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|40% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\40%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 17 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|50% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\50%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 18 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|60% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\60%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 19 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|70% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\70%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 20 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|80% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\80%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 21 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|90% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\90%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 22 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Maximum|100% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Maximum\100%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 23 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|Light Load |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\Light Load\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 24 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|10% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\10%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 25 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|20% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\20%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 26 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|30% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\30%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 27 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|40% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\40%\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 28 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|50% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\50%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 29 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|60% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\60%\report.txt.html |

| Status | PASS |

| Test Time | 15s |

| Test 30 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|70% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\70%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 31 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|80% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\80%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 32 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|90% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\90%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 33 of 34 | top ^ |

| Test Label | Steady-State|Steady-State|Vin Minimum|100% |

| Simulator | simplis |

| Test Report | Steady-State\Steady-State\Vin Minimum\100%\report.txt.html |

| Status | PASS |

| Test Time | 4s |

| Test 34 of 34 | top ^ |

| Test Label | Steady-State|Generate Efficiency Curves |

| Simulator | N/A |

| Test Report | Steady-State\Generate Efficiency Curves\report.txt.html |

| Status | SKIP |

| Test Time | 3s |