SIMPLIS Parts

|

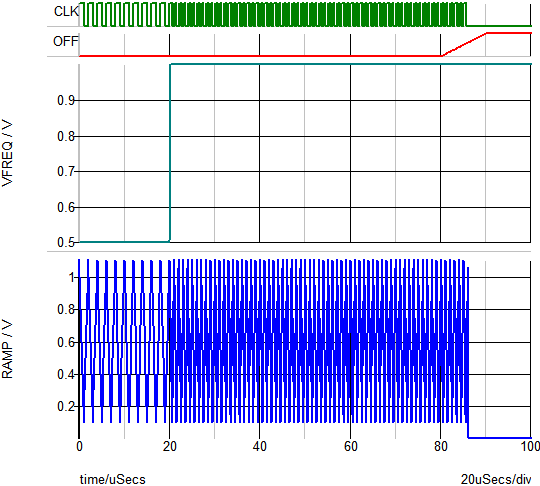

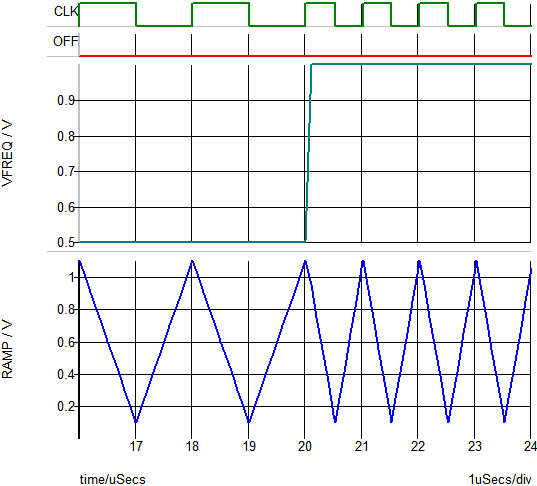

The Voltage Controlled Oscillator w/ 50% Duty Cycle models a VCO with a programmable ramp peak and valley voltages and a voltage-to-frequency gain. This block is speed-optimized for SIMPLIS simulations and can be used as a fixed frequency oscillator by connecting a constant DC voltage source to the frequency pin. The oscillator output ramp waveform is a triangle wave with a 50% duty cycle. This oscillator includes an ON/OFF control pin and outputs commonly used signals that include the following:

For a VCO with a programmable duty cycle, see the Voltage-Controlled Oscillator w/ Programmable Duty Cycle topic.

In this Topic Hide

Model Name: |

Voltage-Controlled Oscillator w/ 50% Duty Cycle |

|

Simulator: |

|

This device is compatible with the SIMPLIS simulator. |

Parts Selector |

Analog Functions | Timing and Oscillators | Simple 50% Duty-Cycle Voltage-Controlled Oscillator (No sync.) |

|

Symbol Library: |

SIMPLIS_BB.sxslb |

|

Model File: |

SIMPLIS_cntl_parts_BB.lb |

|

Subcircuit Name: |

SIMPLIS_VCO_BB |

|

Symbols: |

|

|

Multiple Selections: |

Multiple devices can be selected and edited simultaneously. |

|

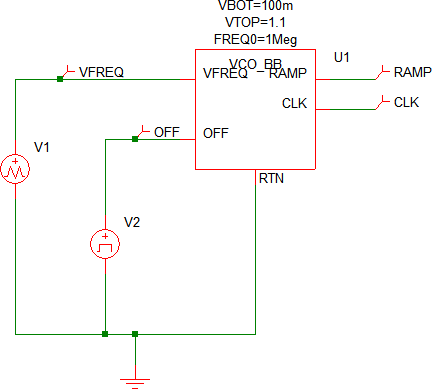

The following table describes the pins on the VCO symbol.

Pin_Name |

I/O |

Function |

Description |

VFREQ |

I |

Input voltage that controls the clock frequency. |

\[ f_{CLK} = VFREQ \times f_0 \] |

OFF |

I |

On/Off control voltage for the oscillator |

Oscillator runs when OFF voltage signal is less than 2.0V.

|

RTN |

|

The circuit return for the VCO |

The ground reference for this circuit |

RAMP |

O |

Saw tooth ramp voltage output |

This output allows you to probe the internal oscillator ramp voltage.

|

CLK |

O |

Digital logic output Logic 0 => CLK = 0V |

The clock frequency is controlled by the VFREQ input. The clock parameters are set in the input dialog box described in Editing_the_VCO.

|

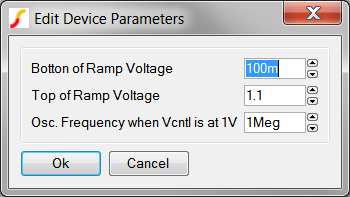

To configure the VCO, follow these steps:

| Label | Parameter Description |

Bottom of Ramp Voltage |

The valley of the ramp voltage |

Top of Ramp Voltage |

The peak of the ramp voltage |

Osc. Frequency when Vcntl is at 1V |

The frequency when VFREQ = 1.0 |

The test circuit used to generate the waveform examples in the next section can be downloaded here: simplis 073 vco 50 duty.sxsch.

© 2015 simplistechnologies.com | All Rights Reserved