» DVM Test Report Overview

| General | |

| Schematic | 6.3_LTC3406B - DVM ADVANCED.sxsch |

| Testplan | dvm_advanced.testplan |

| Original Testplan Filename | 6.4.3_promotescalar_final.testplan |

| Date / Time | 2013-04-25 5:11:52 PM |

| Report Directory | DVM_REPORTS\2013-04-25-5_11_49_PM |

| Log File | dvm_advanced.log |

| # of Tests Run | 2 of 2 (2 of 2 Run, 1 Passed, 1 Failed, 0 Ran with Warnings, 0 Skipped) |

| Total Time | 13s |

| Design Specifications | |

| Circuit Name | LTC3406B |

| Description | Synchronous Buck |

| Input 1 | 5.000 V (4.5 V to 5.5 V) |

| Output 1 | 1.505 V (±5%) @ 1.5 A |

| Switching Frequency | 955kHz |

| Calculated Results | |

| Gain Margin @ 1.505V (dB) | 30.3822 |

| Gain Margin @ 600mV (dB) | 33.8124 |

| Phase Margin @ 1.505V (deg) | 36.9764 |

| phase_margin | 39.8688 |

| Excel-compatible Results | |

| Scalar Results | dvm_advanced_table_scalars.txt |

| Spec Results | dvm_advanced_table_specs.txt |

| Overview Graphs | |

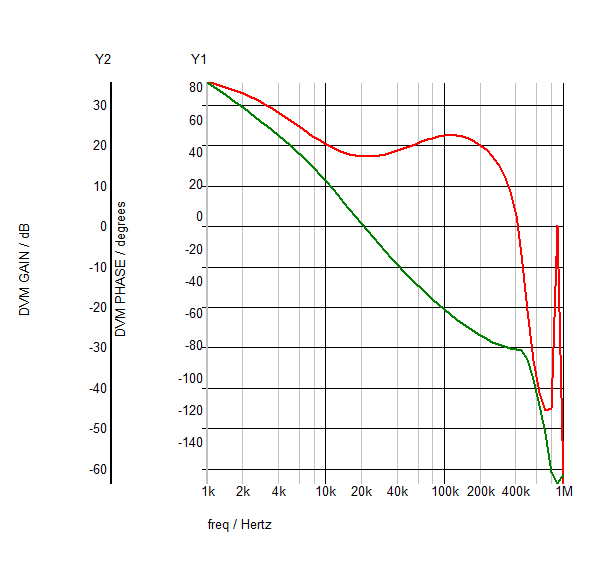

Bode Plot Nominal Vout

GAIN

PHASE

|

|

| SXGPH File | simplis_ac5_224.sxgph |

| Source Test | VOUT=1.505V|Bode Plot|Vin Nominal|50% Load |

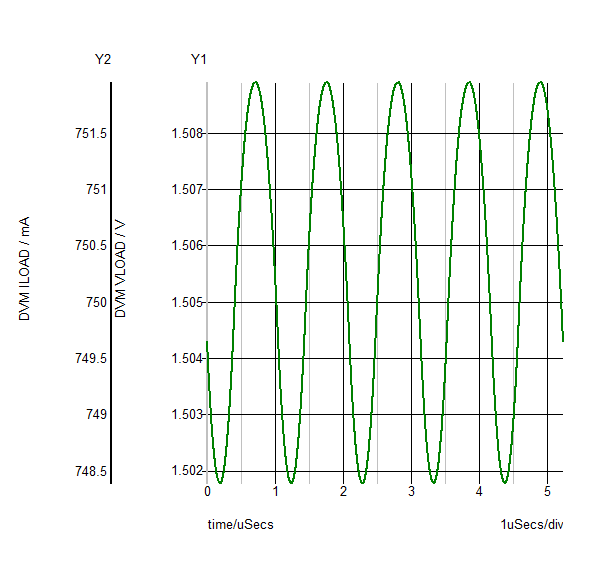

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop5_207.sxgph |

| Source Test | VOUT=1.505V|Bode Plot|Vin Nominal|50% Load |

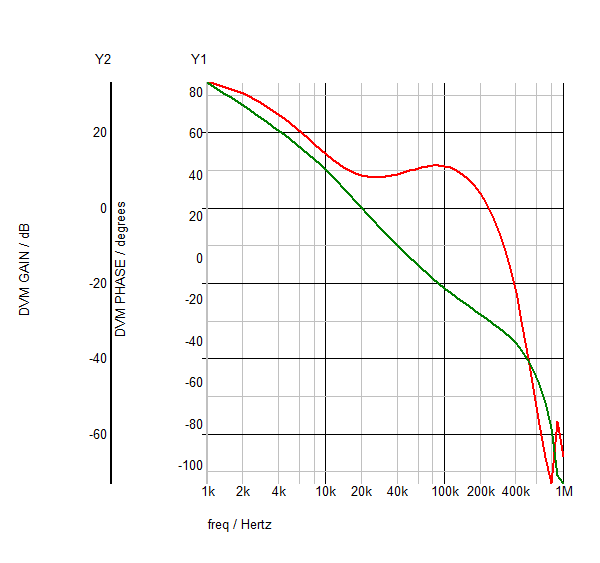

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac6_271.sxgph |

| Source Test | VOUT=0.6V|Bode Plot|Vin Maximum|50% Load |

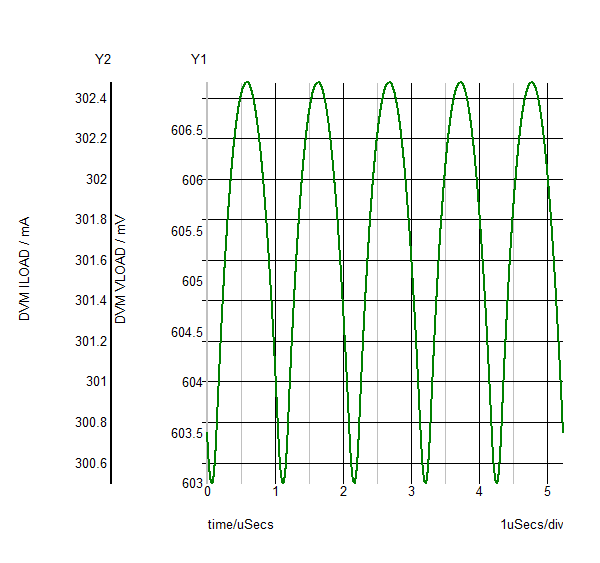

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop6_254.sxgph |

| Source Test | VOUT=0.6V|Bode Plot|Vin Maximum|50% Load |

| Test 1 of 2 | top ^ |

| Test Label | VOUT=1.505V|Bode Plot|Vin Nominal|50% Load |

| Simulator | simplis |

| Test Report | VOUT=1.505V\Bode Plot\Vin Nominal\50% Load\report.txt.html |

| Status | PASS |

| Test Time | 5s |

| Test 2 of 2 | top ^ |

| Test Label | VOUT=0.6V|Bode Plot|Vin Maximum|50% Load |

| Simulator | simplis |

| Test Report | VOUT=0.6V\Bode Plot\Vin Maximum\50% Load\report.txt.html |

| Status | FAIL |

| Test Time | 5s |